## Open-source EDA efforts in Germany: AI HW-SW Co-design and Other Projects

Mehdi Tahoori

CDNC - Chair of Dependable Nano Computing, Department of Computer Science

#### www.kit.edu

Funding program "Design Instruments for Sovereign Chip Develpoment with Open Source (DE:Sign)"

# DE:Sign |Overview

- Design tools, methods and chip designs focussed on open source

- Significant development of the tool chain

- Participation of young academics and talents

- Close collaboration with network "Chipdesign Germany"

- Industry- or science-driven, pre-competitive joint or individual R&D projects

- Universities, research institutions, companies

© Alexander Limbach - AdobeStock

## DE:Sign |Research focus

- a. Open source EDA tools, PDKs und IP libraries

- b. Open source **design methods**

- c. Novel chip designs based on open source EDA tools, PDKs and IP

- d. Design tools, PDKs and IP for **novel technologies**

(e.g. chiplets, advanced packaging, MEMS, radio frequency)

# DE:Sign |Key figures

- Deadline: 31 July 2023

- **Submissions:** 36 pre-proposals with 150 partners (in total)

- Selection meeting: 29 September 2023

- Selection: 15 R&D projects with 62 partners (in total) (thereof 12 industrial partners)

- 11 joint projects, 4 individual projects

- Grant (total): 29.6 Mio. EUR

## DE:Sign |R&D projects open source EDA tools

Talents: Student competition "Open source chip design challenge" (OCDCpro)

| Analog design                                                                                                                                                                        | Hardware security                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>✓ Text based design (ORDeC)</li> <li>✓ High frequency chips (DEMICO)</li> </ul>                                                                                             | <ul> <li>✓ HW architecture (ExViPaS)</li> <li>✓ HW security module (SIGN-HEP)</li> </ul>                                  |

| Digital design                                                                                                                                                                       | Novel technologies                                                                                                        |

| <ul> <li>✓ eFPGAs (OWAS)</li> <li>✓ Verification (OSVISE)</li> <li>✓ FPGAs (FEntWumS)</li> <li>✓ DRAM (DERAMSys)</li> <li>✓ RISC-V (GATE-V)</li> <li>✓ AI hardware (EDAI)</li> </ul> | <ul> <li>✓ RFETs (ReDesign)</li> <li>✓ Radiation resistant HW (Flowspace)</li> <li>✓ Packages/SiP (PASSIONATE)</li> </ul> |

# Open-source Design Tools for Co-development of AI Algorithms and AI Chips DI-EDAI

Bundesministerium für Bildung und Forschung

# Challenges in Attracting Talent for Chip Design

### Long Path to Success

### Mastery Demands

- Requires deep understanding in various subjects

- Deterring rapid-gratification seekers:

- Missing "Hello World" moment for hardware design

### Productivity vs Efficiency

### Software vs Hardware

- Software productivity advancements: Assembly  $\rightarrow$  C/C++  $\rightarrow$  Python

- Hardware's focus on efficiency: hardware programming (languages) are cumbersome

### Salary Gap

- Compensation Disparity

- Lower salaries compared to software/AI

- Dissuades potential talent

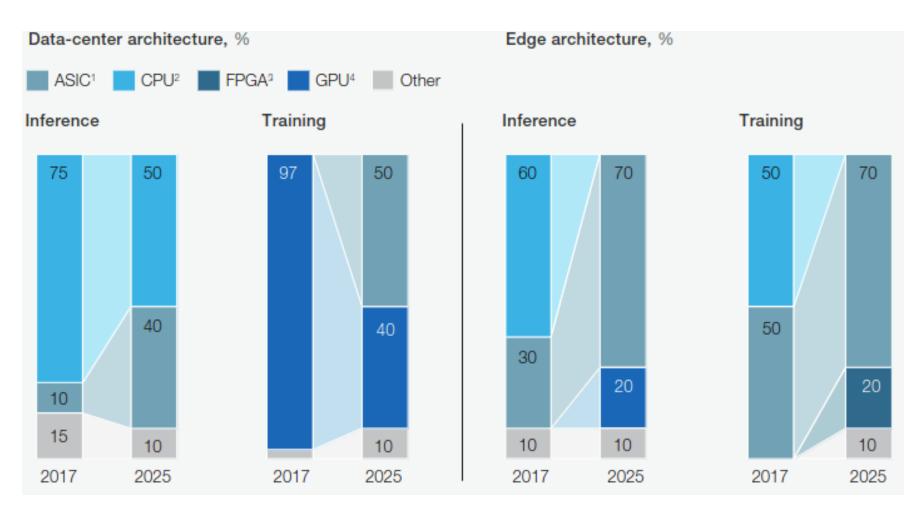

## Shift of preferred HW in data centers and the edge

Source: McKinsey analysis 2018, Artificial-intelligence hardware: New opportunities for semiconductor companies

## **Challenges (and Solutions)**

- Goal: Closing the gap between software and hardware side of AI

- Productivity: like software development

- Efficiency: coming from co-design)

- Sustainability of open-source tools and ecosystems

- How to ensure open source ecosystem survives and thrives beyond initial funding?

- Community building → education and training

- Large user base: heavily used in teaching modules and lab

- Business model around open source hardware EDA and design

### Industry adoption

- **Complementing** rather than competing with existing EDA tools (and industry)

- **Benchmarking**  $\rightarrow$  quantifying added-value

- Path: Academia  $\rightarrow$  SME  $\rightarrow$  (new) large design companies

### Access to restricted technology

- Technology-agnostic design

- Built on top of existing EDA and PDK

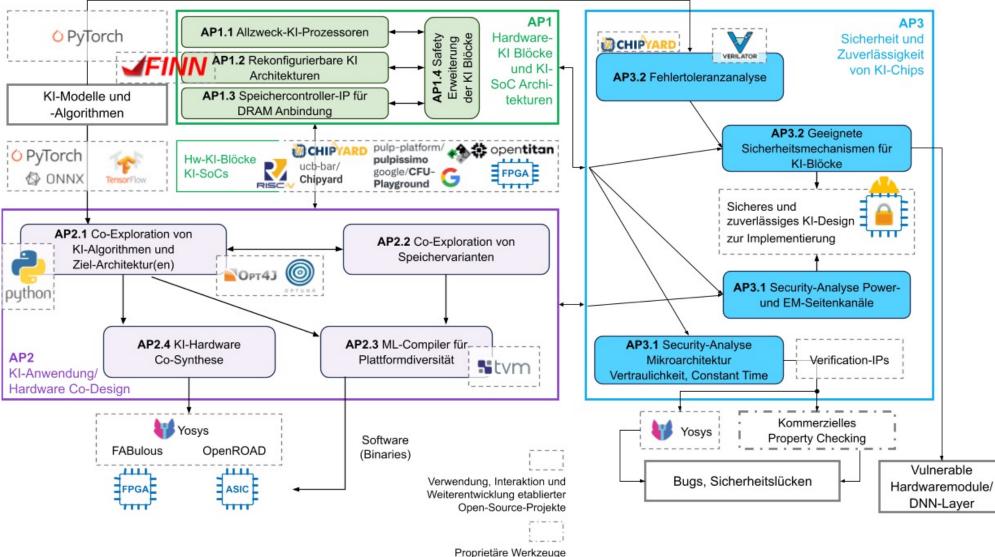

## **EDAI Approach**

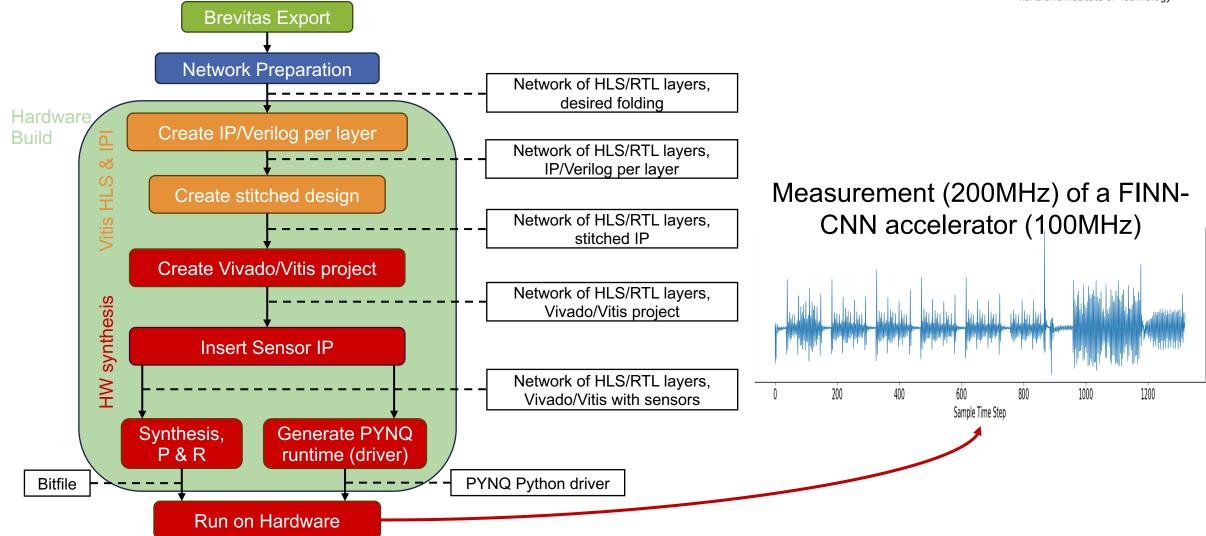

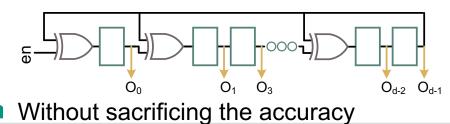

## **Voltage Fluctuation Sensor Integration in FINN**

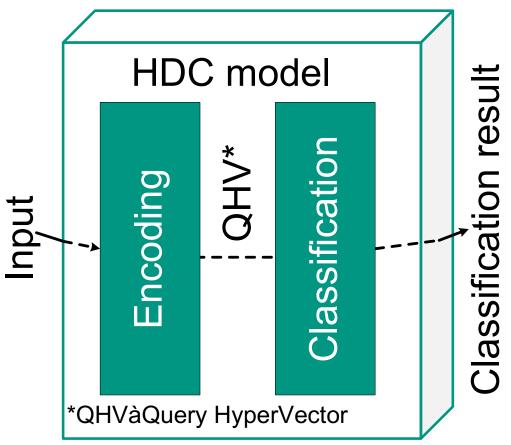

## **Open-Source Hyperdimensional Computing on FPGA**

- A machine learning method

- Can be used on Edge devices i.e, IoTs

- Data and calculations are represented

- In a hyperdimensional space

- Benefits

- Robustness

- Can be trained on small datasets

- Hardware-friendly operations:

- Our extensions

- End-to-end framework, similar to FINN

- Generating encoding parameters On-the-fly at runtime

- Utilizing a combination of well-known cyclic array

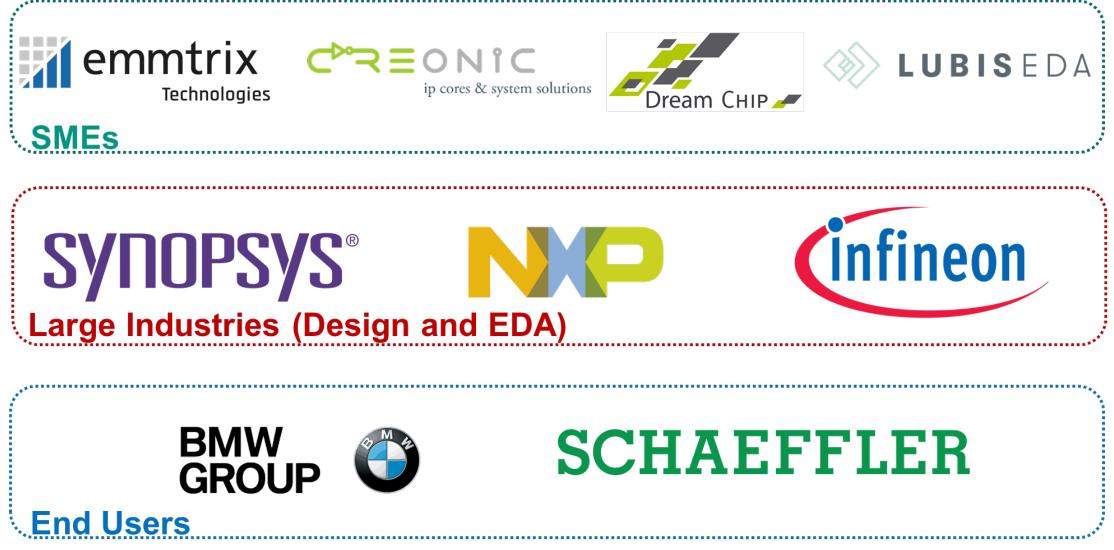

## **Industry Partners**