## EDA-Schema

An Open Graph Datamodel Schema and Dataset for Design Automation

#### **Dr. Ioannis Savidis**

Department of Electrical and Computer Engineering

Drexel University

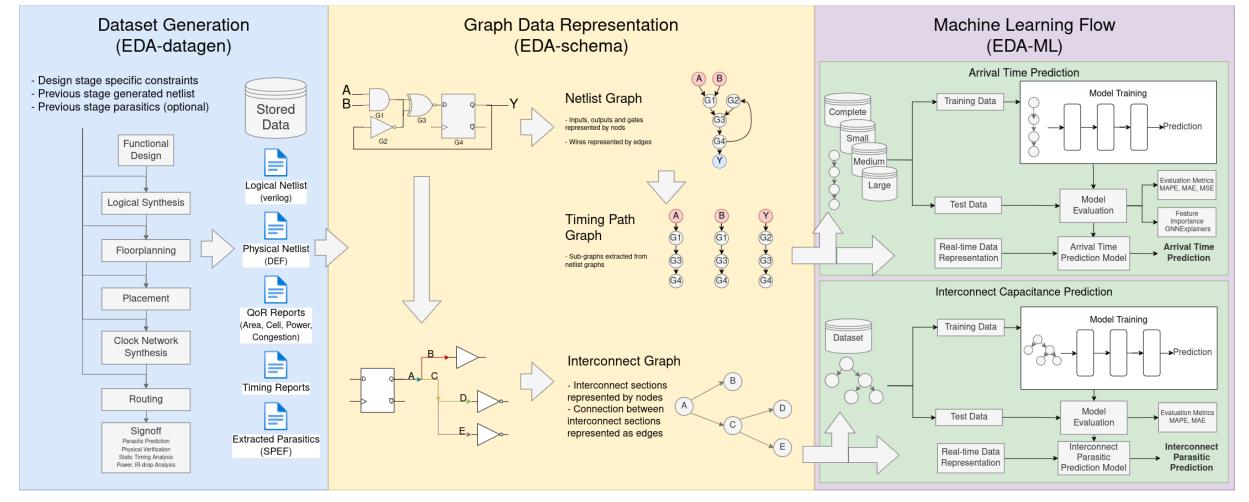

Framework developed within Drexel-ICE to pursue ML problems in EDA

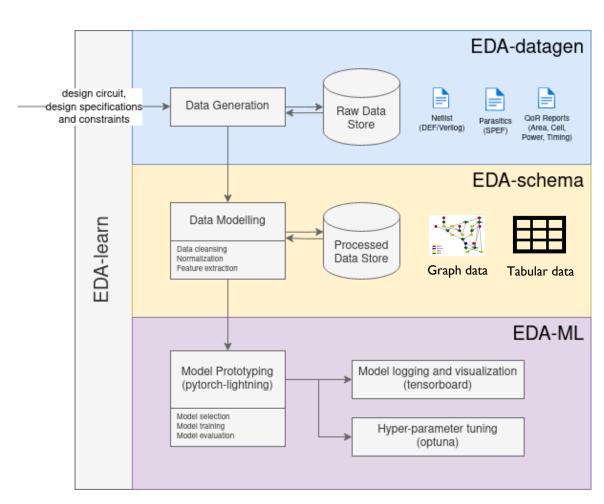

## **Main Components**

- EDA-datagen

- Physical design flow automation for parameterized large scale dataset generation

- EDA-schema

- Property graph data-model schema for circuit data representation

- EDA-ML

- Rapid prototyping and evaluation for EDA based machine learning models

Framework developed within Drexel-ICE to pursue ML problems in EDA

## **Main Components**

- EDA-datagen

- Physical design flow automation for parameterized large scale dataset generation

- EDA-schema

- Property graph data-model schema for circuit data representation

- EDA-ML

- Rapid prototyping and evaluation for EDA based machine learning models

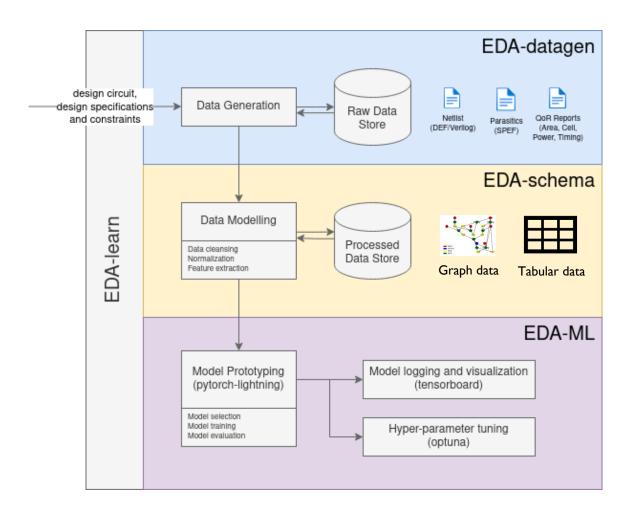

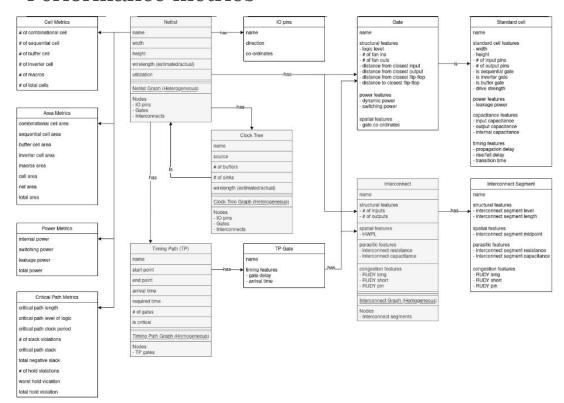

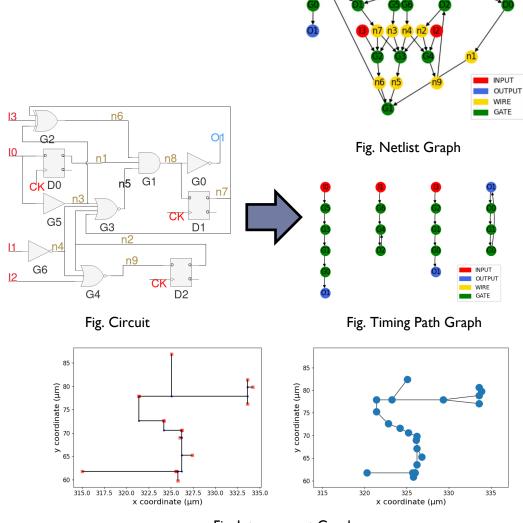

## **EDA Schema**

- Property graph data-model schema incorporating

- Structural data of the circuit

- Performance metrics

Fig. Entity Relationship Diagram

Fig. Interconnect Graph

## EDA Schema: Open Dataset

## Open Dataset

Designs: 20 IWLS'05 benchmark circuits

PDK: Skywater 130nm

Design Toolset: OpenROAD

#### Dataset details

Overall circuits in dataset: 49 \* 20 = 960

• Number of gates in dataset: 7,468,228

• Number of nets in dataset: 7,726,920

Number of timing paths in dataset: 1,561,975

Total dataset size: 82.836G

#### Dataset constraints and parameters

| Parameters                         | Values or Ranges | # of Samples |

|------------------------------------|------------------|--------------|

| Clock periods (ns)                 | {0.5, 1, 2, 5}   | 4            |

| Aspect ratio                       | {0.5, 0.75, 1}   | 3            |

| Max utilization                    | {0.3, 0.5}       | 2            |

| Max skew (ns)                      | [0.01 - 0.2]     | 2            |

| Max fanout                         | [50 - 250]       | 2            |

| Max clock network capacitance (pF) | [0.05 - 0.3]     | 2            |

| Max latency (ns)                   | [0 - 1]          | 2            |

| Total circuits per design          |                  | 48           |

- The dataset is available publicly

- EDA-schema python library allows easy access to the dataset

- https://github.com/drexel-ice/EDA-schema

#### Loading a Netlist

A netlist, identified by attributes such as the circuit name, netlist ID, and design phase, is loaded from the database into an EDA-schema netlist graph object to extract specific details about the digital circuit.

netlist = dataset.load\_netlist({'circuit': 'usb\_phy', 'netlist\_id': 'id-000020', 'phase': 'route'})

## Challenges in ML for EDA: Lack of standardized dataset

- Absence of standardized, open datasets in physical design space is a significant barrier to the advancement and validation of machine learning models

- Key Issues

#### Non-Reproducible Datasets

Researchers rely on custom datasets that are often not reproducible by others, leading to isolated findings and limited scientific validation

## Inconsistent Data Handling

Variability in data preprocessing methods across different studies undermines the ability to compare and validate outcomes effectively

## Challenges in Data Sharing

Creating common frameworks for model architecture and training streamlines development efforts and enhance reproducibility across studies

- Current research based on this flow are

- a) arrival time prediction

b) interconnect capacitance prediction

P. Shrestha, S. Phatharodom, and I. Savidis, "Graph representation learning for gate arrival time prediction," Proceedings of the ACM/IEEE Workshop on Machine Learning for CAD (MLCAD), pp. 127–133, Sept. 2022. P. Shrestha and I. Savidis, "Graph representation learning for parasitic impedance prediction of the interconnect," Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5, May 2023

# Thank You!

Check out our open dataset at

github.com/drexel-ice/EDA-schema