# SiliconCompiler: "Make for HW"

Andreas Olofsson, William Ransohoff, Noah Moroze

Zero ASIC Corporation

Cambridge, MA

{andreas,will,noah}@zeroasic.com

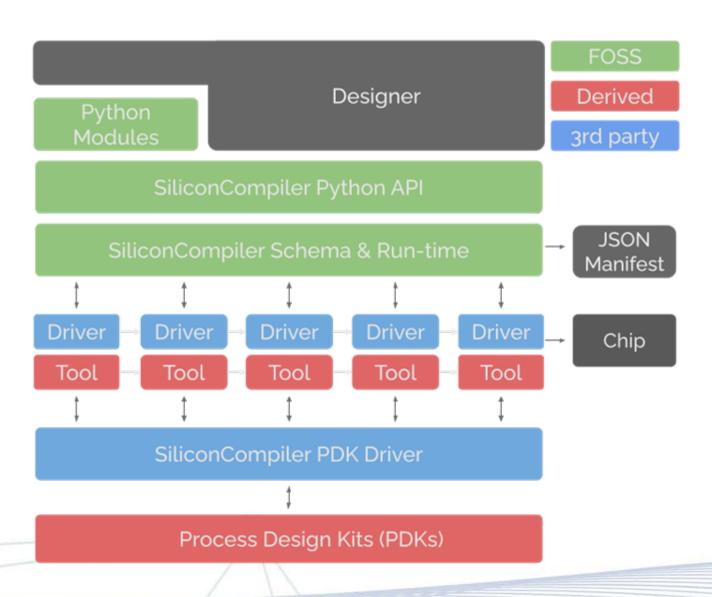

### SiliconCompiler: A modular build system for hardware

- "Make for hardware"

- Standardized build schema (json)

- Python OO API

- Flowgraph based execution

- Developed with cloud first approach

- Automated actions/metrics tracking

- Built for commercial <u>AND</u> open source ASIC/FPGA tools.

- https://github.com/siliconcompiler

### Basic Operation: Configure, Run, Observe

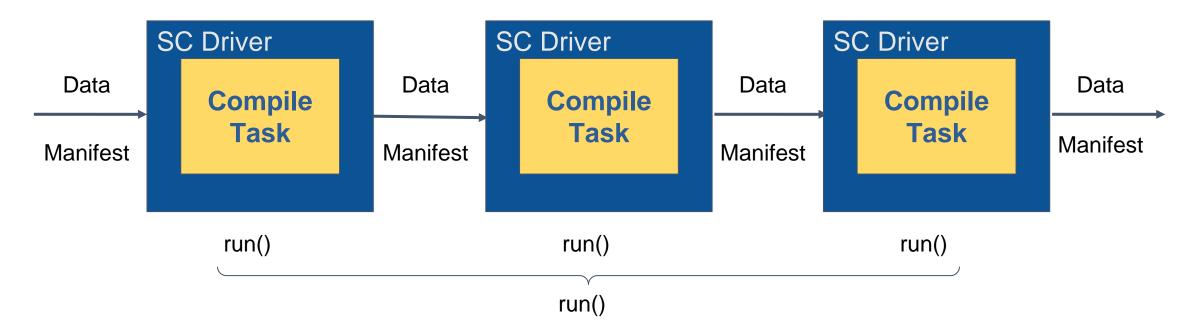

- 1. All compilation tasks (ie EDA tools) are wrapped with SiliconCompiler (SC) interfaces to enable configuration and results tracking in a unified JSON manifest.

- 2. The manifest is the golden database that defines the "what, how, when, who, why" of compilation.

- 3. A static flowgraph defines the sequence of tasks to be executed by the atomic run() function.

- 4. After running, all results and metrics accessible through the manifest.

# The Manifest: An Open "CAD Standard"

| Group         | Parameters | Examples                                        |

|---------------|------------|-------------------------------------------------|

| asic          | 46         | diearea , maxfanout,<br>cell lists, delay model |

| intput/output | 2          | sdc, rtl, def,                                  |

| constraint    | 8          | PVT, SDC, checks,                               |

| options       | 50         | loglevel, skip, optmode, path,                  |

| unit          | 10         | Time, voltage, current,                         |

| pdk           | 50         | Runset, stackup, process,                       |

| tool          | 29         | Options, exename, license,                      |

| flowgraph     | 9          | Inputs, weights, goals                          |

| checklist     | 9          | Rationale, criteria,                            |

| metric        | 45         | Setupwns, errors, warnings,                     |

| datasheet     | 39         | Abs voltage, setup, hold                        |

| package       | 32         | Dependency, author,                             |

- A unified HW compilation manifest

- Standardize all common settings

- Bypass parameters for "one-offs"

- Validated with 5 PDKs, 35 EDA tools,

#### ASIC/FPGA/HLS flows

HOW STANDARDS PROLIFERATE: (SEE: A/C CHARGERS, CHARACTER ENCODINGS, INSTANT MESSAGING, ETC.)

SITUATION:

THERE ARE

14 COMPETING

STANDARDS.

SOON: SITUATION: THERE ARE 15 COMPETING STANDARDS.

# So many options...which is the right one?

#### Manifests:

SC, bender, fusesoc, metrics (openroad), mflowgen, hammer, cadre, orflow, openlane,

bazelhdl, make/homegrown,...

#### Collaborations:

- Openroad Integration: <a href="https://github.com/The-OpenROAD-Project/OpenROAD-flow-scripts/commit/94e9240c7c5297e263cdca862b5c4b1df3fb0111">https://github.com/The-OpenROAD-Project/OpenROAD-flow-scripts/commit/94e9240c7c5297e263cdca862b5c4b1df3fb0111</a>

- Caravael/skywater:

https://github.com/siliconcompiler/siliconcompiler/commit/fcbf3f7f75b786f0577311fc0714d27db0b1faa5

SC is here to stay, not going anywhere!

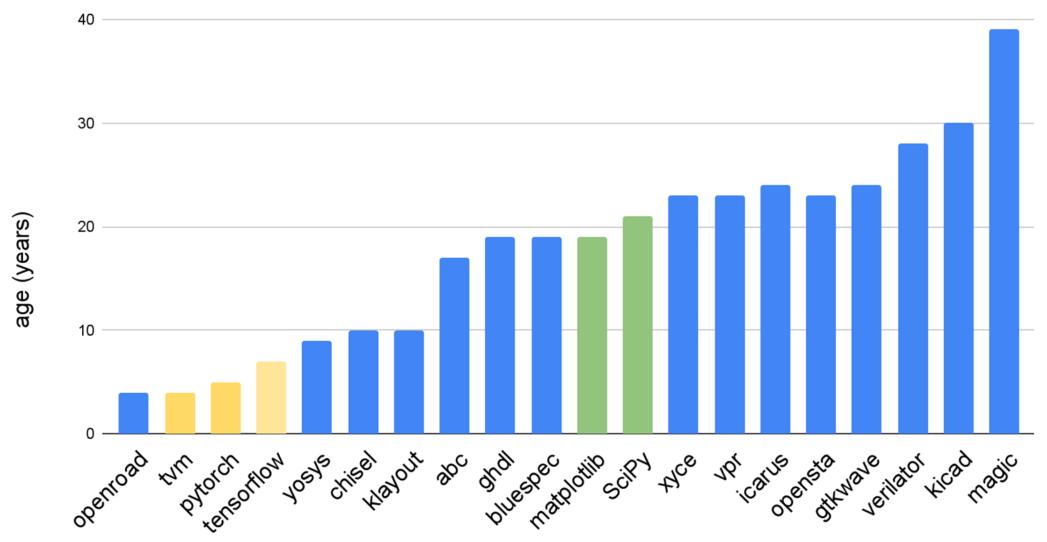

### Reminder: Software is a Lifetime of Maintenance....

#### **Public Service Announcement**

OpenROAD: <a href="https://github.com/The-OpenROAD-Project/OpenROAD">https://github.com/The-OpenROAD-Project/OpenROAD</a>

OpenSTA: <a href="https://github.com/The-OpenROAD-Project/OpenSTA">https://github.com/The-OpenROAD-Project/OpenSTA</a>

Align: <a href="https://github.com/ALIGN-analoglayout/ALIGN-public">https://github.com/ALIGN-analoglayout/ALIGN-public</a>

Magical: <a href="https://github.com/magical-eda/MAGICAL">https://github.com/magical-eda/MAGICAL</a>

ACT: <a href="https://github.com/asyncvlsi/act">https://github.com/asyncvlsi/act</a>

Xyce: <a href="https://github.com/Xyce/Xyce">https://github.com/Xyce/Xyce</a>

SystemC-TLM-lib: <a href="https://github.com/Xilinx/libsystemctlm-soc">https://github.com/Xilinx/libsystemctlm-soc</a>

Pono: <a href="https://github.com/upscale-project/pono">https://github.com/upscale-project/pono</a>

LSOracle: <a href="https://github.com/lnis-uofu/LSOracle">https://github.com/lnis-uofu/LSOracle</a>

OpenFPGA: <a href="https://github.com/lnis-uofu/OpenFPGA">https://github.com/lnis-uofu/OpenFPGA</a>

PRGA: <a href="https://github.com/PrincetonUniversity/prga">https://github.com/PrincetonUniversity/prga</a>

BlackParrot: https://github.com/black-parrot/black-parrot

OpenFASOC: <a href="https://github.com/idea-fasoc/OpenFASOC">https://github.com/idea-fasoc/OpenFASOC</a>

Were IDEA/POSH successful?

Dunno, you be the judge!

Summary of state of EDA/IP...

https://github.com/aolofsson/awesome-hardware-tools

https://github.com/aolofsson/awesome-opensource-hardware