#### **LiveHD and Anubis**

Sakshi Garg, Sheng-Hong Wang, Jing-Hsiang Huang, Hunter Coffman, Rafael T. Possignolo, Akash Sridhar, Kenneth Mayer, and Jose Renau

Department of Computer Science and Engineering

University of California, Santa Cruz

#### **Outline**

Research Problem and Background

LiveHD

-Anubis

Conclusions

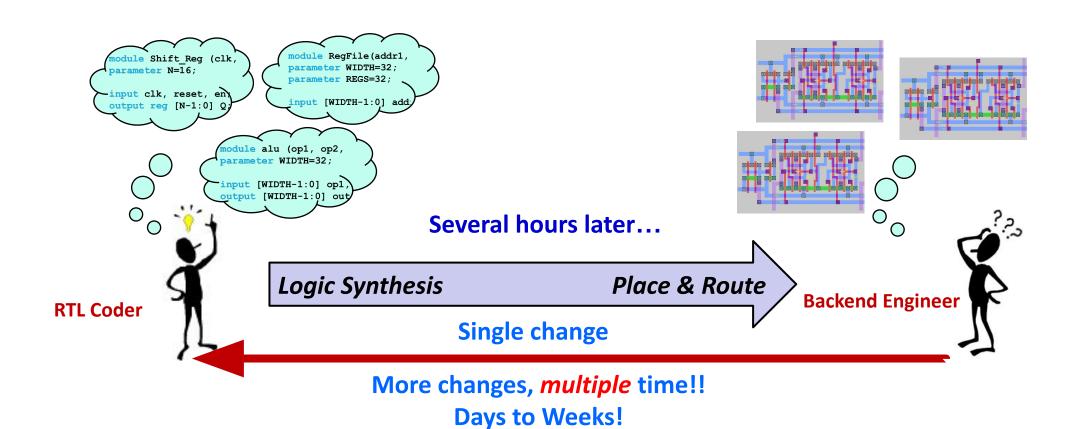

# **Current ASIC/FPGA Flow**

- Re-compiling small design changes ..... takes like forever

- v.s Software development

### **Live Hardware Development**

- LiveHD: incremental and scalable hardware design framework

- incremental: within "seconds", get feedback from small code changes

- scalable: compilation, simulation, and synthesis for large design

- Infrastructures: LLVM-like development ecosystem

- LGraph IR (WOSET'18, 19)

- LNAST IR (WOSET'19)

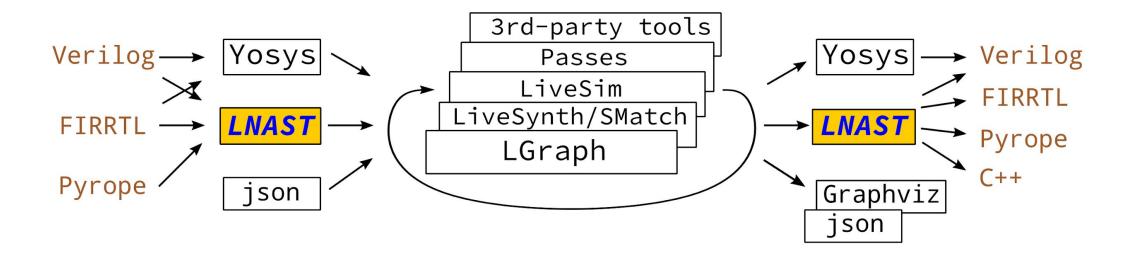

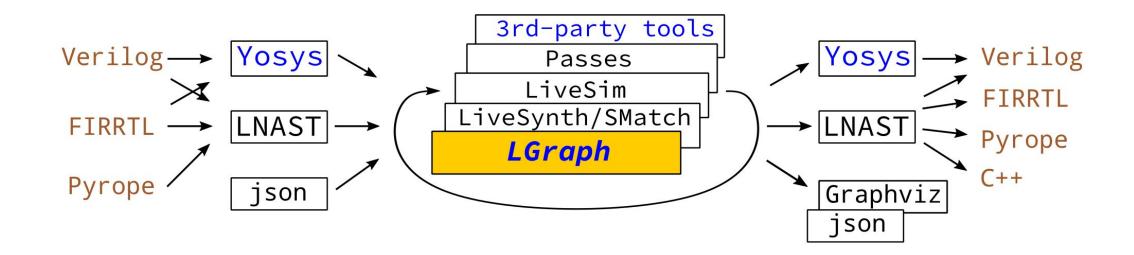

### LiveHD Two Level IRs: LNAST/LGraph

#### **ANUBIS**

- The first benchmark suite intended for evaluating incremental synthesis techniques and flows.

- Goal: Equivalent to the popular SPECint benchmark. typically used to report performance numbers in CPUs

- R.T. Possignolo, N. Kabylkas, J. Renau, "Anubis: A new benchmark for incremental synthesis" International Workshop on Logic and Synthesis '17

#### **Conclusions**

Developing Fast and scalable code base for LiveHD

Developing our Pyrope HDL based on LiveHD

Multi-language interfacing

Moving towards unified compiler for entire hardware design flow

Anubis: To Benchmark the incremental flow

## **Questions?**

https://github.com/masc-ucsc/livehd

https://github.com/masc-ucsc/anubis